Descrizione

L'analizzatore logico PGY-LA-EMBD è il primo analizzatore logico del settore che consente la risoluzione dei problemi di temporizzazione e l'analisi simultanea dei protocolli I2C, SPI, UART, I3C, SPMI, CAN/CAN FD e RFFE nei progetti embedded. Questo ti permette di risolvere rapidamente i problemi a livello di circuito e di sistema. Questo ti permette di eseguire rapidamente il debug dei problemi a livello di circuito e di sistema.

Il PGY-LA-EMBD offre l'acquisizione asincrona dei dati a 1GS/secondo (temporizzazione) e l'acquisizione sincrona dei dati a 100MHz (stato), rendendolo uno strumento di debug ideale per risolvere i problemi dei progetti digitali. I progettisti possono ora analizzare rapidamente i problemi di setup e hold time, i glitch e l'attività dei dati sincroni, oltre ad analizzare i problemi di protocollo.

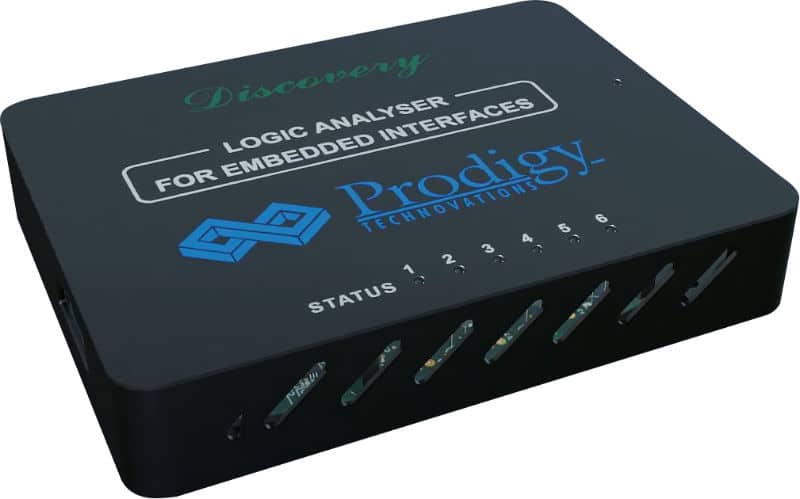

Il Logic Analyser è un analizzatore logico basato su PC progettato per i professionisti più esigenti. Il Discovery Logic Analyser è ideale per la risoluzione dei problemi dei sistemi embedded. L'analizzatore logico ha un fattore di forma molto piccolo, così da poter essere utilizzato per la risoluzione dei problemi in applicazioni mobili. Le funzionalità di decodifica del protocollo sono pensate per la risoluzione di problemi di logica e di protocollo per i team di progettazione embedded nei mercati consumer, industriale, della domotica, della sanità e dell'istruzione.

I progettisti di sistemi embedded devono raccogliere ed elaborare i dati da più interfacce come 2C, SPI, UART, I3C, SPMI, CAN/CAN FD e RFFE per sviluppare una scheda embedded ad alte prestazioni. Il PGY-LA-EMBD decodifica i bus e visualizza l'attività del protocollo con informazioni sul timestamp. Pertanto, è uno strumento ideale per il debug dei problemi di integrazione dell'hardware e del software embedded e per l'ottimizzazione delle prestazioni del software.

I marcatori multipli consentono di effettuare misurazioni delta innovative, fondamentali per gli sviluppatori. La funzione di zoom permette all'utente di visualizzare aree specifiche del segnale.

Caratteristiche Analizzatore logico

- 16 canali con funzione di protocollo e analisi logica.

- 1GS/sec. Analisi dei tempi (asincrona)

- analisi di stato a 100 MHz (sincrona)

- Analisi simultanea dei protocolli I2C-SPI-UART-I3C-SPMI, CAN/CAN FD, e RFFE.

- Funzioni di trigger dettagliate: Auto, pattern, rilevamento del protocollo (I2C, SPI, UART, I3C, SPMI, CAN/CAN FD, RFFE) e temporizzazione (trigger a larghezza di impulso e ritardo).

- Streaming intelligente dei dati del protocollo. Analizzatore per computer host per l'acquisizione a lungo termine tramite interfaccia USB3.0.

- Interfaccia grafica innovativa e facile da usare.

- Analisi degli errori del pacchetto di protocollo

- Fornisce visualizzazioni di tempi, forme d'onda, elenchi e protocolli

- Funzione di filtro dettagliata per i dati decodificati dal protocollo

- Formato di report PDF e CSV.

- Supporto API.

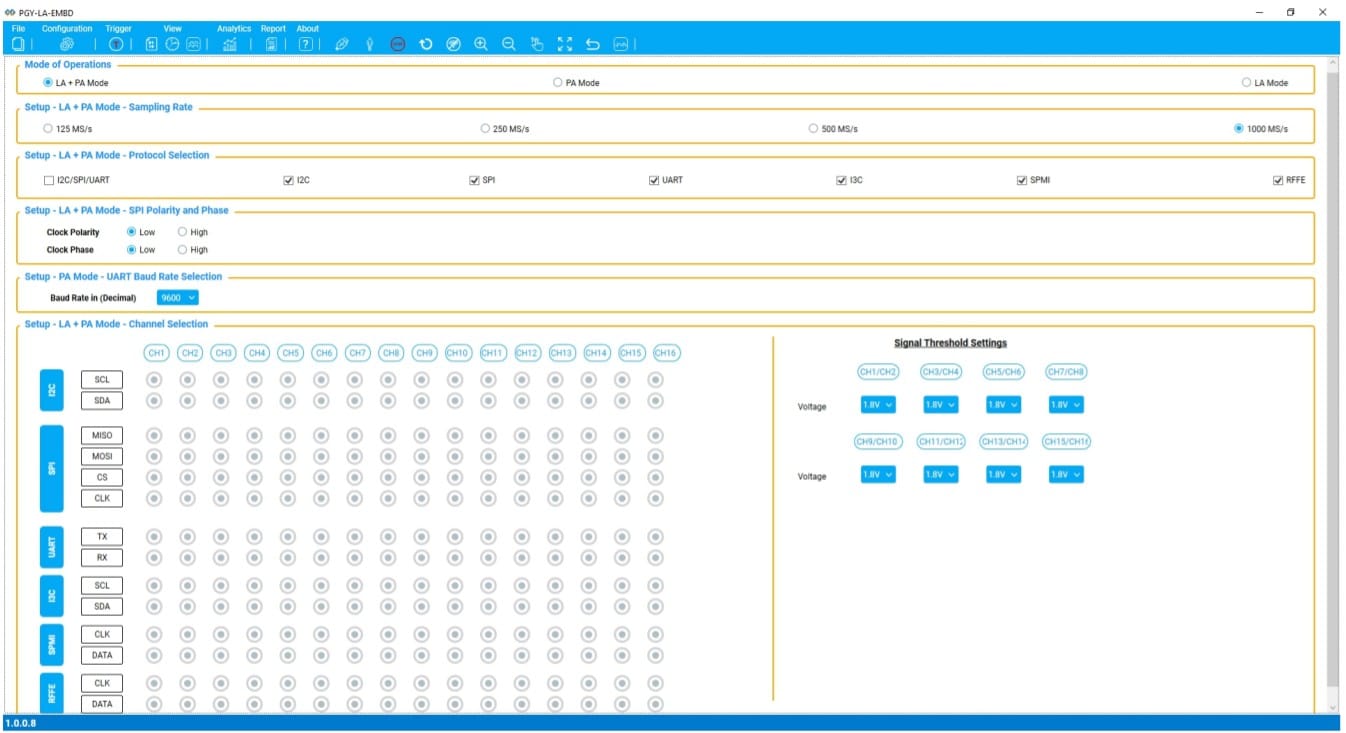

Configurazione semplice

Gli utenti possono configurare facilmente l'Analizzatore Logico per Interfacce Embedded selezionando la modalità Analisi Logica (LA), Analisi Protocollo (PA) o una modalità combinata (LA+PA). Questo permette di configurare il prodotto in modo semplice e veloce e di indagare su problemi complessi a livello di sistema sia con l'analisi logica (analisi degli stati, analisi dei tempi) che con la decodifica del protocollo, o con entrambe. La funzione di salvataggio e recupero garantisce agli sviluppatori la possibilità di recuperare i dettagli di configurazione personalizzati.

Le visualizzazioni multiple del dominio forniscono una panoramica completa delle attività di stato, temporizzazione e protocollo di tutte le interfacce supportate. Gli utenti possono facilmente impostare l'analizzatore per visualizzare le viste di temporizzazione, logica e decodifica del protocollo per facilitare la comprensione del progetto. tramite il menu di configurazione è possibile impostare diverse condizioni di trigger per catturare le attività di temporizzazione e protocollo su eventi specifici. I risultati decodificati possono essere visualizzati nelle finestre Timing, Logic e Log List con autocorrelazione. Questa visione completa delle informazioni lo rende uno dei migliori del settore e fornisce una soluzione facile da usare per il debug dell'attività di protocollo dell'interfaccia embedded e per l'analisi dei problemi di temporizzazione. I cursori multipli aiutano gli sviluppatori a esaminare i dettagli delle prestazioni dei loro progetti.

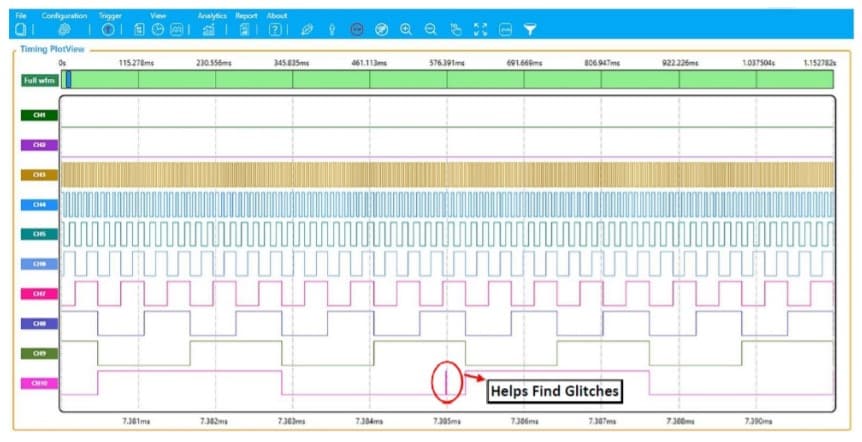

Vista dei tempi

La vista dei tempi è una caratteristica unica del PGY-LA-EMBD che consente ai progettisti di ottenere una visione dettagliata delle informazioni sui tempi dei loro segnali. La Timing View utilizza un segnale di clock interno per rappresentare la forma d'onda. La selezione flessibile della frequenza di campionamento consente agli sviluppatori di analizzare i glitch che possono causare problemi nel funzionamento dei loro progetti. La funzione di raggruppamento permette agli sviluppatori di raggruppare diversi segnali correlati per una migliore visualizzazione e analisi. Le funzioni di marcatura e zoom facilitano l'analisi degli errori di temporizzazione. La possibilità di analizzare qualsiasi punto del set di dati acquisiti garantisce un facile debug e un'analisi su un lungo periodo di acquisizione.

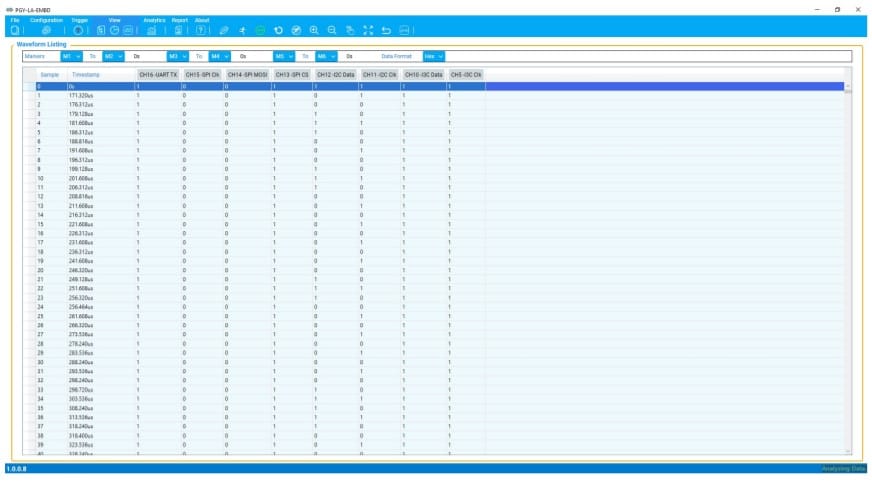

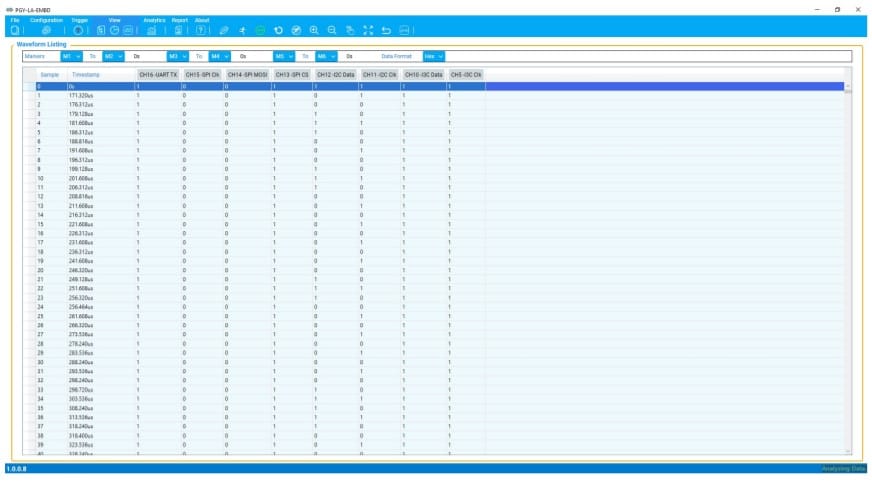

Visualizzazione dello stato/elenco delle forme d'onda

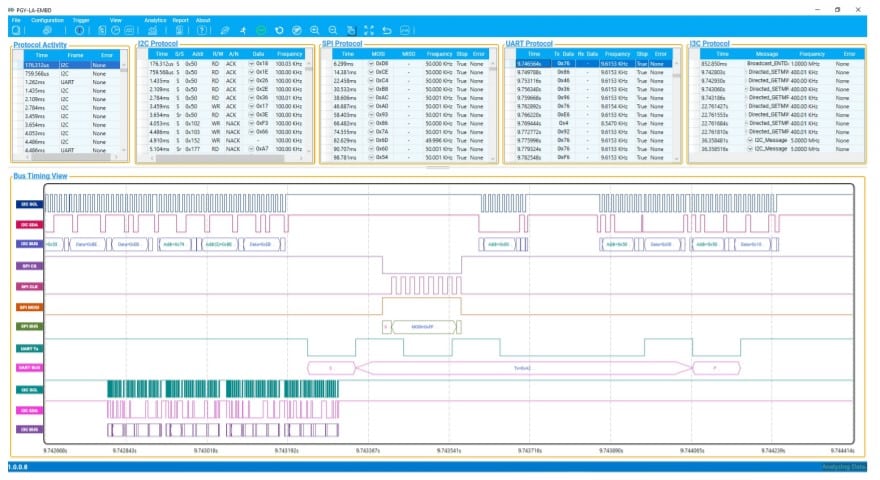

Vista della decodifica del protocollo

La finestra Attività protocollo mostra le informazioni dei pacchetti decodificati in ogni stato e tutti i dettagli dei pacchetti con le informazioni sugli errori. Questo permette ai team di sviluppo di avere una visione a livello di sistema. Le singole finestre di decodifica del protocollo si basano sulle interfacce selezionate e garantiscono una facile visualizzazione per i team di sviluppo. Il fotogramma selezionato nella finestra di elencazione del protocollo viene autocorrelato nella vista dei tempi per mostrare le informazioni sui tempi del pacchetto. Gli errori di protocollo sono evidenziati per garantire che vengano facilmente portati all'attenzione degli sviluppatori.

Potenti funzioni di trigger

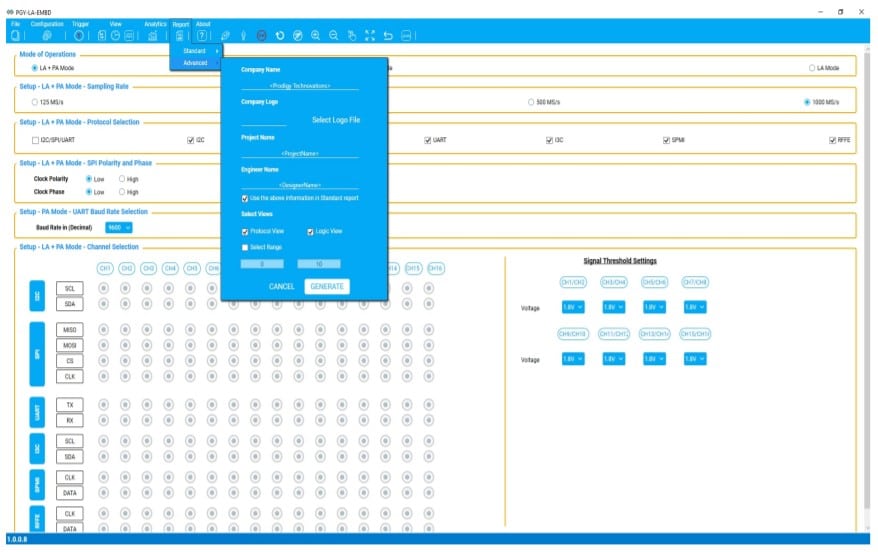

Rapporti

Il report può essere generato in formato PDF o CSV con tutte le informazioni sul segnale, i grafici e i dettagli personalizzati come il nome dell'azienda, il logo, il nome del tester, la data e l'ora per garantire che i progettisti possano documentare tutti i dettagli e condividere il report.

Garanzia

L'hardware e il software sono coperti da una garanzia di un anno. Le sonde sono coperte da una garanzia di tre mesi per tutti i difetti di fabbricazione

Specifiche

| Specifiche tecniche |  |

|---|---|

| Numero di canali | 16 canali logici |

| Velocità di stato | 1GS/s (acquisizione asincrona) |

| Velocità di temporizzazione | Sonde attive a saldare |

| Numero di clock di stato supportati | Secondo, flessibilità di campionamento su fronte ascendente o discendente |

| Lunghezza del set di dati | Streaming continuo intelligente dei dati su HDD/SSD del computer host |

| Supporto del livello di tensione | da 0 a 5 V con la possibilità di definire la soglia logica |

| Grafico della forma d'onda | Visualizza le forme d'onda con un diagramma di bus configurabile in modo flessibile |

| Visualizzazione elenco | Elenco di tutti i campioni di dati in ogni punto di campionamento |

| Trigger per LA | Trigger a schema, trigger a larghezza di impulso, trigger a ritardo |

| Supporto per la decodifica del protocollo | I2C, SPI, UART, I3C, SPMI, CAN/CAN FD, RFFE |

| Decodifica simultanea di I2C, SPI e UART | Sì, collega il bus I2C, SPI e UART all'analizzatore logico. Cattura e visualizza simultaneamente i dati del bus Visualizzazione correlata al tempo con forme d'onda temporali corrispondenti. |

| Visualizzazione del protocollo con visualizzazione dei tempi (PA+LA) | Visualizza simultaneamente i dati decodificati dal protocollo con una frequenza di campionamento elevata e forme d'onda temporali |

| Supporto API | Supporto per automatizzare le operazioni con Python e C++ |

| Tipo di connessione | Sonda volante con prese #16 Micro Grabber Test Clips come accessori opzionali |

| Trigger esterni | Connettore SMA di uscita del trigger |

| Marcatori | Sei, con informazioni delta tra due marcatori. |

| Chiamate | Visualizzazione dei tempi Visualizzazione dell'elenco degli stati/logiche/segnali Visualizzazione del protocollo Diagramma del bus per mostrare i pacchetti del protocollo con il diagramma dei tempi Traccia Auto Trigger - Predefinito (Trigger su qualsiasi pacchetto) |

| Innesco del protocollo | Trigger a schema Trigger consapevole del protocollo- UART: bit di avvio, bit di parità, dati SPI: dati MOSI, dati MISO I2C: bit di START, indirizzo, dati, indirizzo più dati, ACK, NACK, START ripetuto, bit di STOP Parametro di temporizzazione trigger: larghezza dell'impulso (positivo o negativo) Delay trigger. |

| Durata dell'acquisizione | Streaming intelligente dei dati di log su HDD/SSD host. |

| Rapporto | Generazione di rapporti in formato PDF e CSV |

| Connettività host | USB 3.0 Tipo-C |

| Dimensioni | 115 mm x 90 mm x 25 mm |

| Peso | 300 g |

.jpg)

.jpg)

.jpg)

.jpg)