I3C nei dispositivi mobili

Perché l'I3C è necessario?

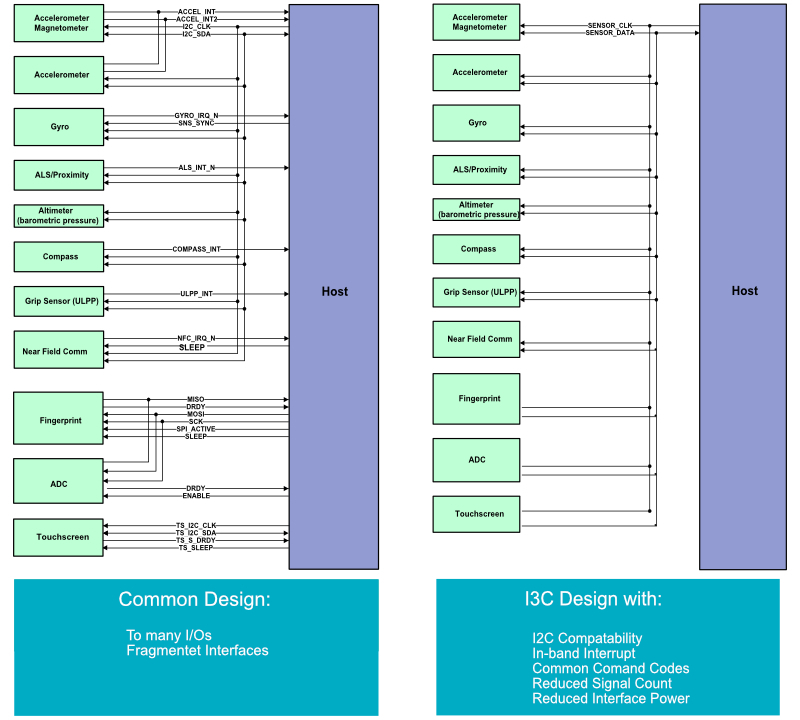

Gli smartphone e gli altri dispositivi dispongono di un numero sempre crescente di sensori meccanici, di movimento, biometrici e ambientali che consentono una serie di funzioni e casi d'uso che le aziende utilizzano per differenziare i loro prodotti. Questa proliferazione di sensori crea notevoli problemi di progettazione, soprattutto per gli sviluppatori di software. Ad esempio, senza un metodo comune di interfacciamento, ogni controller host deve avere il proprio software o driver di sistema per supportare questo hardware. Inoltre, ogni implementazione del controller host può fornire funzionalità e ottimizzazioni diverse.

Cos'è l'I3C e quali sono i suoi vantaggi per gli smartphone?

L'I3C è un'interfaccia bus di utilità e controllo scalabile e ad alta velocità per collegare le periferiche a un processore applicativo, ottimizzando l'integrazione e migliorando l'efficienza dei costi. Offre agli sviluppatori opportunità senza precedenti per creare progetti innovativi per qualsiasi prodotto mobile, dagli smartphone agli indossabili ai sistemi automobilistici.

I3C consente di collegare le periferiche a un processore applicativo in qualsiasi dispositivo mobile, semplificando il processo di connessione e gestione di più sensori in un unico dispositivo. I3C è destinato principalmente ai sensori ad alte prestazioni. Inoltre, I3C trasmette gli interrupt come messaggio nel protocollo senza linee aggiuntive. Con 10,6 MBit/s, I3C supera I2C di oltre tre volte. La modalità ad alta velocità di trasmissione dei dati raggiunge i 33 MBit/s. In alcuni casi, quindi, l'I3C può sostituire la più potente interfaccia periferica seriale (SPI). I vantaggi della specifica I3C sono il minor consumo energetico, il numero ridotto di pin e di percorsi singoli e l'alta velocità di trasmissione con la contemporanea compatibilità con l'I2C. Inoltre, gli indirizzi dei dispositivi possono essere assegnati dinamicamente.

Touch over I3C è un'opzione di interfaccia convergente per i dati tattili elaborati e grezzi. CCI over I3C offre una latenza più bassa e veloce e un controllo più efficiente della telecamera.

Pin di segnale dell'I3C

L'I3C utilizza gli stessi due pin di segnale dell'I²C, denominati SCL (clock seriale) e SDA (dati seriali). La differenza principale è che funzionano sempre come uscite open-drain dell'I²C, quindi la sua velocità è limitata dal conseguente tempo di salita del segnale. L'I3C utilizza la modalità open-drain per compatibilità, ma passa alle uscite push-pull quando possibile e prevede modifiche al protocollo per consentire che ciò avvenga più spesso rispetto all'I²C. SCL è un segnale di clock digitale convenzionale, pilotato dall'attuale master del bus con un'uscita push-pull durante la trasmissione dei dati. (Il clock stretching, una funzione I²C raramente utilizzata, non è supportato) Nelle transazioni con dispositivi I²C slave, questo segnale di clock ha generalmente un ciclo di lavoro di circa il 50%. Tuttavia, quando comunica con slave I3C noti, il master del bus può passare a una frequenza più alta e/o modificare il ciclo di lavoro in modo che il periodo di picco di SCL sia limitato a un massimo di 40 ns. SDA trasmette il flusso di dati seriali, che può essere pilotato sia dal master che dallo slave, ma a una velocità determinata dal segnale SCL del master.

Per la compatibilità con il protocollo I²C, ogni transazione inizia con SDA che agisce come uscita open-drain, il che limita la velocità di trasmissione. Per i messaggi indirizzati a uno slave I3C, la modalità di pilotaggio SDA passa a push-pull dopo i primi bit della transazione, consentendo di aumentare ulteriormente il clock a 12,5 MHz. Questa funzione a media velocità è chiamata modalità SDR (Standard Data Rate). In genere, SDA viene modificato subito dopo il fronte di discesa di SCL e il valore risultante viene ricevuto sul fronte di salita successivo. Quando il master passa SDA allo slave, questo avviene anche sul fronte di discesa di SCL. Tuttavia, quando lo slave restituisce il controllo di SDA al master (ad esempio dopo aver confermato il suo indirizzo prima di una scrittura), rilascia SDA sul fronte di salita di SCL e il master è responsabile di mantenere alto il valore ricevuto per la durata di SCL. (Poiché il master controlla SCL, il fronte di salita viene visualizzato per primo, quindi c'è un breve periodo di sovrapposizione quando entrambi controllano SDA. Tuttavia, poiché entrambi controllano lo stesso valore, non si verifica alcun conflitto di bus)

Framing dell'I3C?

Come I²C, I3C utilizza 9 cicli di clock per inviare ogni byte a 8 bit. Tuttavia, il nono ciclo viene utilizzato in modo diverso. L'I²C utilizza l'ultimo ciclo per un riconoscimento che viene inviato nella direzione opposta a quella dei primi 8 bit. L'I3C funziona allo stesso modo per il primo byte (indirizzo) di ogni messaggio e per i messaggi compatibili I²C. Quando si comunica con gli slave I3C, i byte di messaggio successivi al primo utilizzano il 9° bit come bit di parità dispari in scrittura e come flag di fine dati in lettura. Le scritture possono essere terminate solo dal master. Sia il master che lo slave possono terminare un'operazione di lettura. Lo slave imposta SDA basso per indicare che non ci sono più dati disponibili. Il master prende il controllo di SDA e genera uno STOP o uno START ripetuto. Per consentire la continuazione dell'operazione di lettura, lo slave porta SDA in alto mentre SCL è basso prima del 9° bit, ma lascia SDA fluttuante (open-drain) mentre SCL è alto. Il master può abbassare SDA in questo momento (condizione di START ripetuto) per interrompere l'operazione di lettura.

Nono bit I3C

Come I²C, I3C utilizza 9 cicli di clock per inviare ogni byte a 8 bit. Tuttavia, il nono ciclo viene utilizzato in modo diverso. L'I²C utilizza l'ultimo ciclo per un riconoscimento che viene inviato nella direzione opposta a quella dei primi 8 bit. L'I3C funziona allo stesso modo per il primo byte (indirizzo) di ogni messaggio e per i messaggi compatibili I²C. Quando si comunica con gli slave I3C, i byte di messaggio successivi al primo utilizzano il 9° bit come bit di parità dispari in scrittura e come flag di fine dati in lettura. Le scritture possono essere terminate solo dal master. Sia il master che lo slave possono terminare un'operazione di lettura. Lo slave imposta SDA basso per indicare che non ci sono più dati disponibili. Il master prende il controllo di SDA e genera uno STOP o uno START ripetuto. Per consentire la continuazione dell'operazione di lettura, lo slave porta SDA in alto mentre SCL è basso prima del 9° bit, ma lascia SDA fluttuante (open-drain) mentre SCL è alto. Il master può abbassare SDA in questo momento (condizione di START ripetuto) per interrompere l'operazione di lettura.

Arbitrato del bus I3C

All'inizio di un frame, più dispositivi possono competere per l'utilizzo del bus e il processo di arbitraggio del bus viene utilizzato per selezionare quale dispositivo ottiene il controllo della linea SDA. Sia nell'I²C che nell'I3C, l'arbitrato del bus viene eseguito con la linea SDA in modalità open-drain, consentendo ai dispositivi che trasmettono uno 0 binario (basso) di prevalere sui dispositivi che trasmettono un 1 binario. I dispositivi concorrenti controllano la linea SDA mentre operano in modalità aperta. Modalità drain. Ogni volta che un dispositivo rileva uno stato basso (0 bit) sulla SDA mentre trasmette uno stato alto (1 bit), ha perso l'arbitrato e deve interrompere la competizione fino all'inizio della transazione successiva.

Ogni transazione inizia con l'indirizzo di destinazione e l'implementazione dà priorità agli indirizzi di destinazione con numeri inferiori. La differenza è che I²C non ha limiti sulla durata dell'arbitrato (nella rara ma legale situazione di più dispositivi che cercano di inviare un messaggio allo stesso dispositivo, il conflitto viene rilevato solo dopo il byte dell'indirizzo). Tuttavia, l'I3C garantisce che l'arbitrato sia completato non oltre la fine del primo byte. Questo permette di utilizzare driver push-pull e velocità di clock più elevate per la maggior parte del tempo. Questo avviene in diversi modi: I3C supporta più master, ma non sono simmetrici. Uno è il master corrente ed è responsabile della generazione del clock.

Gli altri dispositivi che inviano un messaggio sul bus (interrupt in-band o master secondari che vogliono utilizzare il bus) devono decidere prima di inviare altri dati utilizzando il proprio indirizzo. Pertanto, non esistono due messaggi legali sul bus che condividano lo stesso primo byte, a meno che il master e un altro dispositivo non stiano comunicando nello stesso momento. L'I3C, come l'I²C, consente l'invio di più messaggi per transazione, separati da simboli "START ripetuti". L'arbitrato è per transazione, quindi i messaggi successivi non sono mai soggetti ad arbitrato. La maggior parte delle transazioni del master I3C inizia con l'indirizzo riservato 0x7E (1111110 2 ).

Poiché questo indirizzo ha una priorità più bassa rispetto a qualsiasi dispositivo I3C, una volta superato l'arbitrato, il master sa che nessun altro dispositivo sta lottando per il bus. Se ai dispositivi I3C vengono assegnati indirizzi bassi come caso speciale (I3C supporta l'assegnazione dinamica degli indirizzi controllata dal master), 0x7E il master sa che l'arbitrato, una volta che l'indirizzo ha vinto l'arbitrato per un numero di bit iniziali sufficiente a distinguerlo da un indirizzo assegnato, è completo e può passare al funzionamento push-pull su SDA. Se tutti gli indirizzi assegnati sono inferiori a 0x40, questo avviene dopo il primo bit. Se tutti gli indirizzi sono inferiori a 0x60, questo avviene dopo il secondo bit e così via.

Nel caso descritto sopra, in cui il master corrente inizia una transazione con l'indirizzo di un dispositivo che sta lottando per l'utilizzo del bus, entrambi trasmettono i loro byte di indirizzo con successo. Tuttavia, ognuno si aspetta che l'altro confermi l'indirizzo (abbassando SDA) per il successivo bit di conferma. Di conseguenza, nessuno dei due si accorgerà della mancanza di conferma. In questo caso, il messaggio non verrà inviato, ma il master vincerà l'arbitrato: eventualmente verrà inviato un inizio ripetuto, seguito da un tentativo, che avrà successo.

Codici di comando generali

Una scrittura indirizzata all'indirizzo riservato 0x7E viene utilizzata per eseguire una serie di operazioni speciali in I3C. Tutti i dispositivi I3C devono ricevere e interpretare le scritture indirizzate a questo indirizzo oltre che ai loro indirizzi individuali. In primo luogo, una scrittura composta solo dal byte dell'indirizzo e da nessun byte di dati non ha alcun effetto sugli slave I3C, ma può essere utilizzata per semplificare l'arbitrato I3C. Come descritto in precedenza, questo prefisso può accelerare l'arbitrato (se il master supporta l'ottimizzazione della commutazione push-pull dei midbyte) e semplifica il master evitando un caso di arbitrato un po' complicato. Se la scrittura è seguita da un byte di dati, questo byte codifica un "codice di istruzione generale", un'operazione I3C standardizzata. I codici di comando 0-0x7F sono comandi broadcast diretti a tutti gli slave I3C.

Possono essere seguiti da parametri aggiuntivi specifici del comando. I codici di comando 0x80-0xFE sono comandi diretti a singoli slave. Sono seguiti da una serie di START ripetuti e dalla scrittura o dalla lettura di specifici slave. Durante l'esecuzione di un comando diretto, le operazioni di scrittura o lettura trasmettono i parametri specifici del comando per ogni slave. Questa operazione sostituisce la normale risposta dello slave a un messaggio I3C. Un comando diretto può essere seguito da diversi messaggi per slave, ciascuno preceduto da uno START ripetuto. Questa modalità speciale termina alla fine della transazione (simbolo STOP) o al successivo messaggio indirizzato a 0x7E . Alcuni codici di comando esistono sia in forma broadcast che diretta. Ad esempio, i comandi per attivare o disattivare gli interrupt in banda possono essere inviati a singoli slave o inviati a tutti. I comandi per recuperare i parametri da uno slave (ad esempio il comando GETHDRCAP per chiedere a un dispositivo quali modalità ad alta velocità di trasmissione dati sono supportate) esistono solo in forma diretta.

Opzioni HDR (High Data Rate)

Ogni transazione sul bus I3C inizia in modalità SDR, ma il master I3C può emettere un comando broadcast CCC "Enter HDR" che informa tutti gli slave I3C che la transazione continuerà in una specifica modalità HDR. Gli slave I3C che non supportano l'HDR possono quindi ignorare il traffico sul bus fino a quando non vedono una sequenza specifica "HDR Exit" che li informa che è arrivato il momento di ascoltare nuovamente il bus. (Il master sa quali sono gli slave che supportano l'HDR e quindi non tenterà mai di utilizzare l'HDR per comunicare con uno slave che non lo supporta) Alcune modalità HDR sono compatibili anche con i dispositivi I²C se questi ultimi hanno un filtro di picco di 50ns nella linea SCL. Ciò significa che ignorano un livello alto sulla linea SCL che dura meno di 50 ns. Questa caratteristica è richiesta dalle specifiche I²C, ma non è universalmente implementata e non tutte le implementazioni ignorano i picchi ripetuti di frequente.

Pertanto, è necessario verificare la compatibilità con l'I3C HDR. Le modalità HDR compatibili utilizzano impulsi SCL di 45 ns o meno, quindi i dispositivi I²C li ignorano. La modalità HDR DDR utilizza una segnalazione a doppia velocità di dati con un clock di 12,5 MHz per ottenere una velocità di dati grezzi di 25 Mbit / s (in realtà 20 Mbit / s). Ciò richiede la modifica della linea SDA mentre SCK è alto, una violazione del protocollo I²C, ma i dispositivi I²C non vedono il breve impulso alto su SCL e quindi non notano la violazione. Le modalità HDR-TSP e HDR-TSL utilizzano uno dei tre simboli come cifre ternarie (trits):

Una transizione da SDA e SCL (ricevuti entro 12,8 ns l'uno dall'altro), Solo una transizione da SCL o Solo una transizione da SDA. Due byte più due bit di parità (18 bit in totale) sono divisi in sei triplette da 3 bit e ogni triplette è codificata come due trits. A una velocità di 25 Mtrit/s, si ottiene una velocità di trasmissione dati effettiva di 33,3 Mbit/s. La coppia di trits composta da due sole transizioni da SDA non viene utilizzata per la codifica dei dati, ma per il framing che segna la fine di una sequenza HDR. Anche se questo limita il tempo massimo tra le transizioni SCL a tre volte il trit, questo supera il limite di 50ns dei vecchi dispositivi I²C. Pertanto, la modalità HDR TSP (simbolo ternario, puro) può essere utilizzata solo su un bus senza dispositivi I²C più vecchi. Per consentire l'utilizzo di bus con dispositivi I²C (con un filtro di picco), è necessario utilizzare la modalità HDR-TSL (simbolo ternario, legacy). Questo mantiene la compatibilità I²C grazie al trit stuffing: se dopo un fronte di salita su SCL il trit successivo non è 0, il trasmettitore inserisce un trit 1 (transizione solo su SCL) che viene ignorato dal ricevitore. In questo modo si garantisce che SCL non sia mai alto per più di un tempo di trit.

Classi di dispositivi

Su un bus I3C in modalità standard (SDR) possono essere supportate quattro diverse classi di dispositivi:

- Master principale I3C

- Master secondario I3C

- Slave I3C

- Slave I²C (dispositivi più vecchi).

Le seguenti funzioni I²C non sono supportate in I3C

Le resistenze di pull-up sono fornite dal master I3C. I resistori di pull-up esterni non sono più necessari. Clock Stretching - I dispositivi devono essere sufficientemente veloci per funzionare alla velocità del bus. Il master I3C è l'unica fonte di clock. Indirizzi I²C estesi (10 bit). Tutti i dispositivi su un bus I3C sono indirizzati con un indirizzo a 7 bit. I dispositivi I3C nativi hanno un indirizzo unico a 48 bit che viene utilizzato solo per l'assegnazione di indirizzi dinamici.

Interfaccia del controller host I3C

I3C HCI definisce un insieme comune di funzioni per il controller host e l'interfaccia software che può essere utilizzato per creare definizioni di classi basate su un insieme comune di funzioni. La definizione consente estensioni e ottimizzazioni specifiche per i fornitori, in modo da integrare più facilmente funzioni a valore aggiunto per smartphone, wearable, Internet of Things (IoT), automobili e altro ancora. La specifica fornisce al software della piattaforma un mezzo efficiente per comunicare con le funzioni del dispositivo master sul bus I3C e garantisce il funzionamento a basso consumo del controller host. Il risultato finale è che gli sviluppatori hanno il tempo di concentrarsi sull'integrazione di fotocamera, touch e altri componenti e funzioni per differenziare i loro prodotti. "

I3C Touch e Camera

I3C contiene numerose specifiche progettate appositamente per il settore mobile. Queste estensioni delle specifiche per casi d'uso specifici vanno, ad esempio, dalla connettività touch alla fotocamera e consentono agli sviluppatori una più facile implementazione e un risparmio sui costi di sviluppo.

I3C HCI è anche inclusa nella famiglia di specifiche I3C touch, in modo che i comandi touch e i flussi di dati multipli possano essere utilizzati per aggiungere funzionalità touch differenziate a un progetto. Le aziende produttrici di processori applicativi possono applicare la specifica per standardizzare il metodo HCI utilizzato nei loro dispositivi. La specifica definisce diverse ottimizzazioni basate sull'uso tipico. Ad esempio, la funzione di comando combinato permette di trasferire in modo efficiente una sola volta i trasferimenti di scrittura e poi di lettura sul bus. Un altro esempio è il comando automatico che può leggere in modo efficiente un buffer di dati di grandi dimensioni nel contesto degli interrupt in-band.

Analizzatore di protocollo I3C e adattatore host

PGY-I3C-EX-PD è lo strumento leader che permette ai progettisti e agli ingegneri di test di verificare i progetti I3C secondo le loro specifiche configurando PGY-I3C-EX-ED come master/slave, generando traffico I3C con funzione di iniezione di errori e decodificando i pacchetti di decodifica del protocollo I3C.