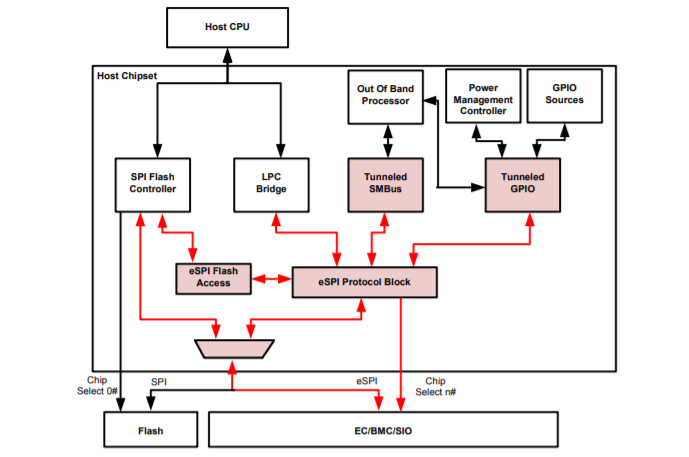

Interfaccia periferica seriale avanzata (eSPI)

Il leader del settore Intel definisce il nuovo standard eSPI come un miglioramento delle transazioni di dati con un consumo energetico e costi inferiori. I produttori possono integrarlo facilmente - a livello di chip, scheda e sistema - nei loro prodotti.

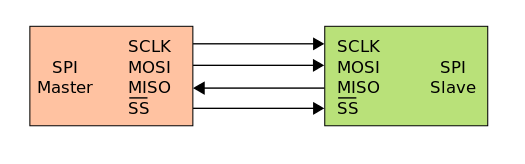

Base SPI

I dispositivi SPI comunicano in modalità full duplex utilizzando un'architettura master-slave (terminologia alternativa come principale e secondario) con un unico master. Il dispositivo master crea il frame per la lettura e la scrittura. I dispositivi slave multipli sono supportati dalla selezione di linee slave select (SS) individuali, talvolta chiamate linee chip select (CS).

Funzioni

In totale, le funzioni di comprendono un'interfaccia a quattro fili (ricezione, trasmissione, clock e selezione dello slave) e tre configurazioni:

- IO singolo (o IO standard): Clock, Chip-select, segnale dati unidirezionale (MOSI), segnale dati unidirezionale (MISO)

- DUAL IO: Clock, Chip-select, segnale dati bidirezionale (IO0), segnale dati bidirezionale (IO1)

- QUAD IO: Clock, Chip-select, segnale dati bidirezionale (IO0), segnale dati bidirezionale (IO1), segnale dati bidirezionale (IO0=2), segnale dati bidirezionale (IO3)

eSPI: quali sono i vantaggi rispetto agli altri sistemi bus?

Con un livello di tensione significativamente più basso, da 1,8 V a 3,3 V, un numero ridotto di pin e una frequenza operativa due volte più veloce, 66 MHz rispetto a 33 MHz, i progressi tecnici del nuovo standard eSPI sono enormi. Grazie a questi vantaggi tecnici, eSPI è destinata a sostituire l'interfaccia LPC (lower pin count), utilizzata nel mercato dei computer da oltre 15 anni e considerata lo standard comune.

Il livello di segnale più basso riduce la potenza richiesta. Inoltre, sopprime il rumore del segnale che spesso si verifica a velocità di clock più elevate. Il numero ridotto di pin riduce il numero di tracce necessarie sul PCB. eSPI richiede un massimo di 8 pin per uno slave: chip select, clock, 4 linee di dati, allarme (opzionale) e reset.

La velocità di clock accelerata consente una maggiore larghezza di banda per il trasferimento dei dati e operazioni più veloci: 4x 66 MHz.

Per soddisfare i requisiti del prodotto, i progettisti di sistemi possono selezionare la frequenza di clock massima da supportare: 20, 25, 33, 50 o 66 MHz.

Grazie alla stabilità di uno standard definito a livello industriale, l'eSPI può supportare lo sviluppo futuro delle piattaforme client e server, comprese le periferiche e la memoria, per molti anni a venire.

soluzione di analisi del protocollo eSPI

2.550,00 €*

Disponibile, tempo di consegna: 1 -3 giorni